静电卡盘高压多区独立PID纹波抑制系统

在半导体先进制造、平板显示以及高精度真空镀膜工艺中,静电卡盘作为晶圆或基板的非接触式夹持工具,其性能直接关系到工艺均匀性与产品良率。通过施加数百至数千伏直流高压,ESC利用介电材料的极化效应或约翰逊-拉贝克效应产生强大的静电吸附力,将基片平整、牢固地固定于卡盘表面。随着器件特征尺寸进入亚纳米时代,对于晶圆局部平坦度、热传递均匀性以及工艺过程中应力控制的要求达到近乎严苛的程度。传统的单区或简单分区静电卡盘已难以满足需求,高压多区独立控制ESC应运而生。它将卡盘背面的电极分割成数十甚至数百个可独立寻址的微小单元,通过为每个单元施加独立可调的高压,实现对吸附力分布的精细调控,从而主动补偿晶圆翘曲、优化传热或进行局部工艺修正。然而,多区独立高压控制带来了一个基础性挑战:如何确保每一路高压输出都具有极高的直流纯净度,即极低的纹波。任何残留的交流纹波都会转化为吸附力的周期性脉动,可能诱发晶圆的高频微振动,影响光刻套刻精度,或在薄膜沉积、刻蚀工艺中引入不可接受的均匀性波动。因此,一套针对多区高压输出的精密“PID纹波抑制系统”成为高端静电卡盘电源的核心技术模块。

在静电卡盘应用中,高压纹波的来源是多方面的。首先,为多个高压通道供电的主电源架构,无论是集中式高压生成后分配,还是分布式独立模块化设计,其前级的AC-DC变换或DC-DC变换过程都会引入开关噪声。其次,每个高压通道的本地DC-HV转换电路(如使用Cockcroft-Walton倍压电路或高频逆变升压)在工作时也会产生特有的纹波频率成分。再者,多路高压输出之间的相互串扰、负载(卡盘电极与晶圆构成的容性负载)的动态变化以及外部电磁环境干扰,都可能耦合进输出高压中,形成复杂的纹波频谱。这些纹波通常表现为叠加在直流高压上的、从几十赫兹到数百千赫兹不等的周期性电压波动。

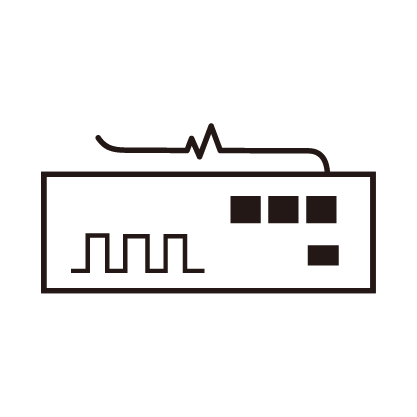

PID控制,作为一种经典且强大的闭环控制算法,被引入到每一路高压输出的纹波抑制环节中。其基本思想是:通过高精度高压分压器或差分探头,实时采样该路输出的实际电压值。将采样值与内部设定的纯净直流参考值进行比较,得到误差信号。该误差信号(包含了直流偏差和纹波成分)被送入PID控制器。PID控制器中的比例项对当前误差做出即时反应;积分项累积历史误差以消除稳态直流偏差;而关键的微分项或通过适当设计的滤波器,可以对误差的变化趋势(即纹波的斜率)做出预测性补偿。控制器的输出经过功率驱动后,用于调节高压生成电路中的关键元件(如PWM占空比、线性调整管的栅极电压等),从而产生一个与纹波相位相反、幅度相当的补偿信号,最终在输出端实现纹波的抵消。

将PID纹波抑制应用于“多区独立”高压系统,复杂性显著增加。首先,每一路高压通道都需要一套独立的电压采样、PID计算和功率调节回路。这意味着需要数十上百套并行的、高性能的模拟前端和数字控制器。这些控制器必须具有足够高的采样率和运算速度,才能有效抑制高达数百千赫兹的纹波频率。其次,通道间的独立性必须得到保障。一套通道的补偿动作不应通过共地、共电源或空间耦合的方式干扰到相邻通道。这要求电源系统在布局布线、接地策略和电磁屏蔽上进行极其考究的设计。例如,采用星型接地、为每个通道配备独立的隔离电源和数字隔离通信接口是常见做法。

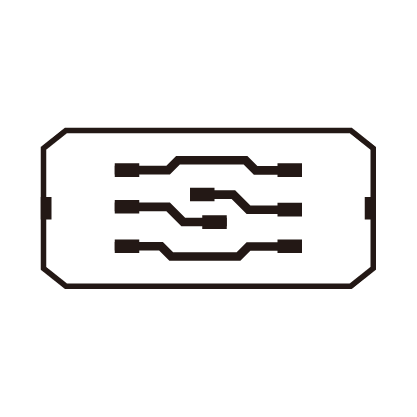

再者,PID参数的整定成为一项艰巨任务。每一路高压通道由于其负载电容的微小差异、布线电感的不同以及元器件参数的分散性,其传递函数(从控制输入到电压输出的关系)略有不同。因此,理想情况下,每一路都需要独立进行PID参数(比例系数Kp、积分时间Ti、微分时间Td)的整定,以实现最优的纹波抑制效果和环路稳定性。在数百个通道的系统中,手动整定不现实,必须依赖自动化的闭环辨识与参数整定算法。系统在上电或定期维护时,可能自动向各通道注入微小的测试信号,测量其频率响应,并据此计算或优化出一组合适的PID参数。

此外,系统还需要应对动态负载变化。在工艺过程中,晶圆与卡盘之间的接触状态、局部温度变化导致的介电常数微变,都可能引起负载阻抗的动态波动,从而改变纹波特性和环路增益。一个鲁棒性强的PID控制器或结合了自适应算法的进阶控制器,需要能够在一定范围内适应这种变化,维持纹波抑制性能。

静电卡盘高压多区独立PID纹波抑制系统的最终效能,体现在输出电压的纹波系数上。高端系统要求在全电压范围、全负载条件下,输出直流高压的峰峰值纹波低于0.1%甚至0.01%。这相当于将数千伏高压中的交流波动压制在几伏甚至几百毫伏以内。如此高的纯净度,确保了静电吸附力在时间和空间上的绝对稳定,为亚纳米级光刻、原子层沉积等超精密工艺提供了不可或缺的静态与动态夹持基础。这套系统是模拟电路设计、数字信号处理、控制理论和高压工程深度融合的产物,是现代半导体装备追求极致工艺窗口的一个缩影。