静电卡盘射频干扰抑制高压设计

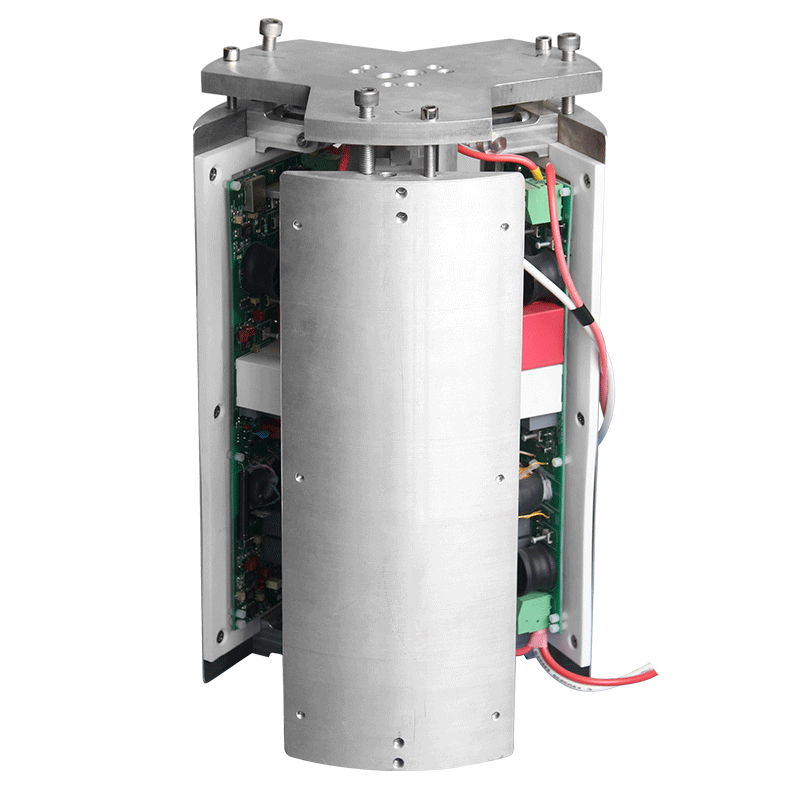

在现代等离子体工艺设备,如刻蚀机和化学气相沉积设备中,静电卡盘已成为固定晶圆的主流方案。它通过向内部电极施加数百至数千伏的直流高压,在卡盘表面与晶圆背面之间产生强大的静电场,借助约翰逊-拉贝克力或库仑力吸附住晶圆。同时,为了实现工艺所需的离子轰击或等离子体激发,卡盘通常还集成有射频偏压电极,用于向晶圆施加数十至数百伏的射频功率。这种直流高压与射频功率共存的工况,对为静电卡盘提供吸附力的直流高压电源提出了极其严峻的挑战:如何在高强度、宽频谱的射频电磁干扰环境中,稳定、可靠、精确地输出并维持所需的高压。射频干扰抑制能力,已成为衡量静电卡盘高压电源设计水平的关键标尺。

射频干扰主要通过传导和辐射两种途径耦合进高压电源系统。传导干扰经由高压输出电缆、低压电源线及信号线侵入;辐射干扰则穿透电源机箱的缝隙或直接作用于内部电路。这些干扰会带来一系列问题:首先是高压输出的稳定性被破坏。射频噪声叠加在直流高压上,会导致实际施加在卡盘电极上的电压含有大幅度的交流分量,这不仅可能降低有效吸附力,引起晶圆滑移,更可能在吸附界面上引发微放电,损伤晶圆背面或卡盘介电层。其次,干扰可能使电源内部的电压、电流采样信号严重失真,导致闭环控制回路误判,引发输出电压异常振荡或失控。最严重的情况是,强大的射频能量可能直接耦合进电源的功率开关器件或控制芯片,造成器件过热损坏或逻辑错误,导致电源故障停机,进而引发工艺腔室破真空等重大生产事故。

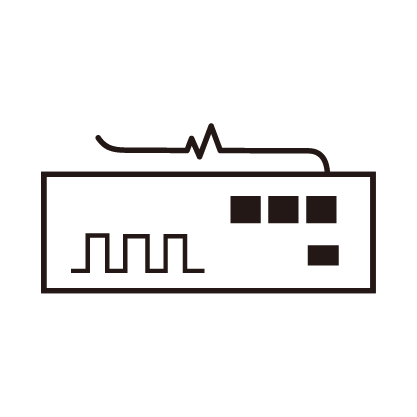

因此,静电卡盘高压电源的设计,必须将射频兼容性置于核心位置,实施从系统架构到元件布局的全方位干扰抑制策略。首先在输入输出端口,必须部署针对射频频段(通常为数百kHz到上百MHz)的高性能滤波器。输入端的交流电源滤波器需能有效抑制从电网传入的射频噪声,同时防止电源自身的开关噪声污染电网。更为关键的是高压输出回路的滤波设计。由于输出电缆在射频场中相当于天线,必须在电源输出端口和卡盘接口处均设置滤波网络。这种网络通常由特殊设计的高压射频抗流圈和穿心电容构成,形成多级低通滤波,旨在让直流或低频控制信号(如用于调节吸附力的电压变化)畅通无阻,而对MHz级别的射频信号呈现极高的阻抗,将其阻隔在电源主体之外。滤波器的设计必须考虑卡盘的等效电容和电缆的分布参数,确保在宽频带内具有稳定的衰减特性,避免在某些频率点发生谐振导致干扰放大。

其次,电源内部的电路布局与屏蔽至关重要。所有对噪声敏感的模拟控制电路、采样电路和基准源,必须被安置在独立的、具有连续电磁密封的屏蔽腔内。高压生成与变换部分,如高频变压器、功率开关管等强干扰源,也应进行局部屏蔽。电源机箱应采用导电性良好的材料,所有盖板与箱体之间使用射频屏蔽衬垫,确保缝隙的电磁泄漏最小化。内部连接线,尤其是采样反馈线,应尽可能短,并使用屏蔽双绞线,屏蔽层单点接地以避免地环路。电源的接地策略需要精心规划,通常采用“星形”单点接地系统,将数字地、模拟地、功率地、机壳地最终汇集到一点,防止射频噪声通过地线耦合。

在电路设计层面,需采用对射频干扰不敏感的拓扑和控制方法。例如,在高压生成部分,优先采用谐振或软开关技术,这不仅可以降低开关损耗,更能显著减小开关电压和电流的dv/dt和di/dt,从而从源头上降低高频电磁干扰的强度。电压和电流采样电路应使用差分输入、高共模抑制比的隔离放大器,并配合有效的低通滤波和数字平均算法,从被噪声污染的原始信号中提取出真实的直流分量。数字控制器的软件中需植入强大的抗干扰算法,如看门狗、指令冗余、数据校验等,防止程序跑飞。

此外,高压电源与设备主控系统的通信接口也需加强防护。常用的模拟量(0-10V/4-20mA)控制信号应使用屏蔽电缆,并在两端加装滤波磁珠或瞬态抑制二极管。数字通信接口(如RS-485、以太网)则应采用光耦隔离或光纤传输,彻底切断传导干扰路径。

一套经过精心射频设计的静电卡盘高压电源,其性能需要在真实的等离子体环境中进行验证。测试时,应在其输出端连接模拟卡盘负载,并在近距离施加与实际工艺相同功率和频率的射频功率。然后监测高压电源输出的纹波噪声系数、长期漂移、动态响应以及自身工作的稳定性。优秀的电源应能在这种严苛的电磁环境下,保持输出电压精度优于±0.5%,纹波有效值低于0.1%,并且不发生任何误报警或保护性关机。

总而言之,为等离子体设备中的静电卡盘配备高压电源,其挑战远不止于提供稳定的千伏电压。它本质上是一场与高强度射频干扰的“静默战争”。成功的“射频抑制高压设计”,要求工程师深刻理解电磁兼容理论,并具备从宏观系统架构到微观电路板布局的全方位设计能力。这样的电源,才能确保晶圆在狂暴的等离子体环境中被牢牢吸附、精确控温,为高端的半导体制造工艺提供坚实、无声的基础。它是设备稳定运行的幕后守护者,其可靠性直接关系到生产线的稼动率与产品良率。