高压信号发生器的频率合成技术升级

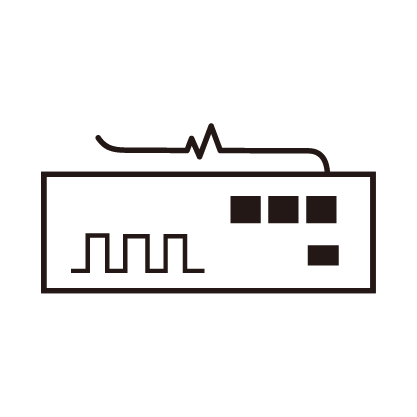

高压信号发生器作为雷达测试、通信设备校准、电磁兼容(EMC)测试等领域的核心仪器,其输出信号的频率精度、相位噪声、频率分辨率直接影响测试结果的准确性。传统高压信号发生器的频率合成技术多采用锁相环(PLL)或直接数字合成(DDS),PLL 技术存在相位噪声高、频率切换速度慢的问题,DDS 技术则受限于输出频率上限(通常低于 1GHz),难以满足高频、高精度测试需求,频率合成技术升级成为突破这一局限的关键。

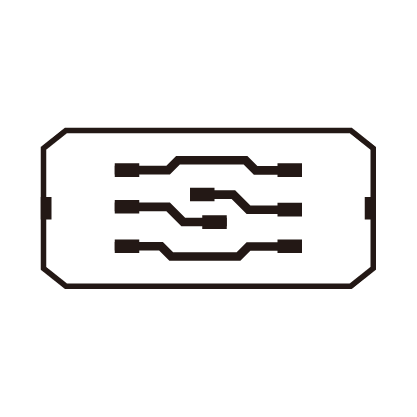

本次升级以 “PLL + DDS 混合合成” 为核心架构,结合小数分频、相位噪声抑制、宽频段扩展技术,实现高频段与高精度的协同优化。在核心合成架构上,采用 DDS 作为基准信号源,利用其高频率分辨率(可至 1Hz 以下)的优势,生成低频段(0.1Hz - 100MHz)高精度信号;通过倍频器(采用 GaAs 工艺的倍频芯片)将 DDS 输出信号倍频至高频段(100MHz - 10GHz),再与 PLL 技术结合,利用 PLL 的高频率稳定性,对倍频后的高频信号进行相位锁定,抑制倍频过程中引入的相位噪声。该混合架构既保留了 DDS 的高分辨率,又突破了 DDS 的频率上限,使信号发生器输出频率范围扩展至 0.1Hz - 10GHz。

在相位噪声优化方面,从硬件与软件两方面入手。硬件上,选用低噪声晶振(相位噪声≤-150dBc/Hz@1kHz 偏移)作为参考时钟,采用屏蔽腔体设计隔离参考时钟模块与功率模块,减少电磁干扰;在 PLL 环路中,选用低噪声鉴相器与环路滤波器,优化环路带宽(设置为参考时钟频率的 1/100 - 1/200),使 PLL 的相位噪声在 1kHz 偏移时降至 - 130dBc/Hz 以下。软件上,采用相位噪声补偿算法,通过实时采集输出信号的相位信息,对 DDS 的相位累加器进行动态校正,进一步降低相位噪声(补偿量可达 5 - 10dB)。

频率分辨率与切换速度的提升是升级的另一重点。采用小数分频 PLL 技术替代传统整数分频,通过小数分频器实现非整数倍的频率分频,使频率分辨率从 100Hz 提升至 1Hz;引入快速锁定算法,优化 PLL 的电荷泵电流与环路滤波器参数,使频率切换时间从 10ms 降至 1ms 以内,满足动态测试场景需求。此外,针对高压输出需求,在频率合成后增加高压放大模块,采用推挽式功率放大电路,选用高压耐流晶体管,使输出信号的峰值电压从 100V 提升至 1kV,同时保证信号失真度(THD)小于 1%,满足高压测试场景(如高压设备绝缘测试)的信号需求。

升级后的高压信号发生器在雷达测试中,可生成 10GHz 高频信号,频率分辨率达 1Hz,相位噪声≤-125dBc/Hz@1kHz 偏移,满足雷达接收机灵敏度测试需求;在 EMC 测试中,1kV 高压信号可模拟强电磁干扰环境,为设备抗干扰性能测试提供精准信号源。频率合成技术的升级使高压信号发生器的性能指标显著提升,适配更多高端测试场景。