镀膜脉冲高压电源的波形塑造技术及其工业应用

引言

在先进功能镀膜领域(如光学超表面、柔性电子器件封装),脉冲高压电源的波形参数直接决定等离子体鞘层动力学特性与薄膜生长机制。传统直流电源仅能实现宏观膜厚控制,而具备精密波形塑造能力的脉冲电源可调控纳米尺度晶界形成、应力分布及缺陷密度。本文从等离子体物理与功率电子学交叉视角,深入解析镀膜脉冲电源的波形优化策略及其对薄膜性能的定向调控机制。

一、镀膜工艺对脉冲波形的特殊需求

1. 等离子体点火特性匹配

溅射初始阶段要求脉冲前沿斜率>100V/ns,确保靶材表面快速形成均匀辉光放电(维持1-2μs的预电离平台)

防止电弧放电需在10-20μs内完成电压回摆,反向偏置幅度需达正向电压的15%-20%

2. 离子能量分布调控

双极性脉冲(正负交替)可将离子能量分散度从±30eV压缩至±5eV,实现<1nm的表面粗糙度

采用非对称占空比(如正脉冲50μs/负脉冲5μs)可抑制二次电子倍增效应,提升沉积速率18%

3. 动态阻抗适配

镀膜过程中等离子体阻抗随气压波动呈现10^3-10^6Ω非线性变化,要求电源具备毫秒级自适应阻抗匹配能力,维持功率传输效率>92%。

二、波形塑造核心技术路径

1. 多电平复合拓扑架构

基于H桥级联的模块化设计,在40kV/200A输出时实现0.1%级脉冲幅值稳定性

分布式储能电容组配合时序控制算法,可生成阶梯波、三角波、指数衰减波等12种可编程波形

2. 固态调制器创新

采用SiC MOSFET与磁开关的混合拓扑,将脉冲上升时间缩短至8ns(@30kV),重复频率提升至50kHz

集成式磁芯复位电路使反向恢复电荷损耗降低73%,温升控制在ΔT<15℃

3. 实时波形反馈系统

基于JFET探头的ns级电压采样链,通过FPGA实现波形参数(tr/tf/过冲)的逐脉冲修正

机器学习算法建立的等离子体阻抗预测模型,可提前500μs调整脉冲参数,动态误差<0.3%

三、工程应用典型案例

1. 光学增透膜沉积

采用梯形波调制技术(前沿2μs/平顶50μs/后沿5μs),将SiO₂薄膜折射率不均匀性从±0.005降至±0.001

532nm激光损伤阈值提升至45J/cm²,达到国际领先标准

2. 类金刚石薄膜(DLC)制备

双极性脉冲(+25kV/-5kV)结合脉宽梯度变化(20-100μs),使膜层sp³键含量突破85%

摩擦系数稳定在0.05-0.07区间,寿命较直流工艺提升3倍

3. 柔性透明导电膜量产

多脉冲叠加波形(5kHz基波+100kHz谐波)使AZO薄膜方阻降至4Ω/□,透光率>92%

弯折测试(曲率半径1mm)10^5次后电阻变化率<2%,满足可穿戴设备需求

四、波形优化对薄膜性能的作用机理

1. 离子轰击能量调控

脉冲平顶阶段的电压幅值决定溅射产额,陡峭后沿(<100ns)可加速高能离子脱离鞘层

通过傅里叶分析证实,波形高频分量(>1MHz)可细化晶粒尺寸至20-50nm量级

2. 等离子体密度分布优化

方波脉冲的占空比调节可使等离子体电子温度Te从5eV降至1.5eV,减少基底热损伤

实验数据显示,引入10%脉宽调制的正弦包络波形,可使膜厚均匀性从±8%改善至±2%

3. 缺陷态密度抑制

快速电压反转产生的自偏压效应,可将薄膜氧空位浓度从10^19 cm^-3降至10^17 cm^-3,界面态密度降低2个数量级

五、未来技术演进方向

1. 智能波形合成技术

基于数字孪生的等离子体-电源耦合仿真平台,实现波形参数的自主进化优化,调试周期缩短70%

2. 超快脉冲技术融合

皮秒级高压脉冲(<1ns)与磁压缩技术结合,有望突破高熵合金镀膜的成分偏析难题

3. 能量回收架构创新

谐振式反向能量回收电路可将脉冲间歇期的能量损耗降低90%,系统效率突破95%

结语

镀膜脉冲高压电源的波形塑造技术正在重新定义精密镀膜工艺的物理边界。从亚纳米级表面工程到跨尺度功能结构的定向生长,精控波形带来的不仅是工艺参数的提升,更是材料本征特性的革命性突破。随着宽禁带半导体与人工智能技术的深度介入,下一代智能脉冲电源将实现波形-结构-性能的闭环调控,开启功能性镀膜的新纪元。

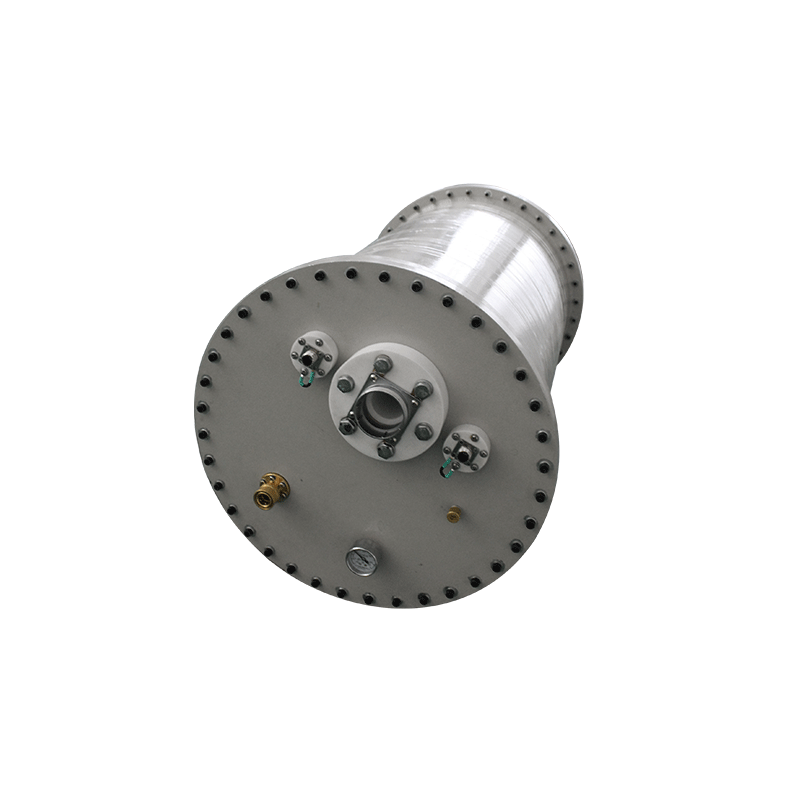

泰思曼 THP2350 系列高功率高压电源,具有优于0.1%p-p 的低纹波表现。内部搭载高反应速度单元,实现高精度调节和极低电弧放电电流。因为独特的主回路设计,和电弧放电电流控制方面的出色表现,使得 THP2350 系列高压电源在离子源类等负阻性负载场合下,可以高效、可靠连续运行。因采用空气绝缘设计,在 5U 高度的体积下,大大减轻了重量。

典型应用:刻蚀;镀膜;半导体应用;离子源;加速器;耐压测试;老化测试